الفيزياء الكلاسيكية

الفيزياء الكلاسيكية

الكهربائية والمغناطيسية

الكهربائية والمغناطيسية

علم البصريات

علم البصريات

الفيزياء الحديثة

الفيزياء الحديثة

النظرية النسبية

النظرية النسبية

الفيزياء النووية

الفيزياء النووية

فيزياء الحالة الصلبة

فيزياء الحالة الصلبة

الليزر

الليزر

علم الفلك

علم الفلك

المجموعة الشمسية

المجموعة الشمسية

الطاقة البديلة

الطاقة البديلة

الفيزياء والعلوم الأخرى

الفيزياء والعلوم الأخرى

مواضيع عامة في الفيزياء

مواضيع عامة في الفيزياء|

أقرأ أيضاً

التاريخ: 2025-01-23

التاريخ: 7-4-2021

التاريخ: 13-10-2021

التاريخ: 6-5-2021

|

في كثير من التطبيقات يتم وصل مجس رقمي إلى دارة رقمية لقياس كمية معينة. فإذا كانت طبيعة هذا المجس رقمية فإنه يمكن وصله مع الدارة الرقمية التي تعالج الإشارة الناتجة منه بسهولة. فعلى سبيل المثال وصل مفتاح on-off أو مرحل أو مرمز (encoder) يكون سهلا؛ وذلك لأن هناك حالتين إما on أو off.

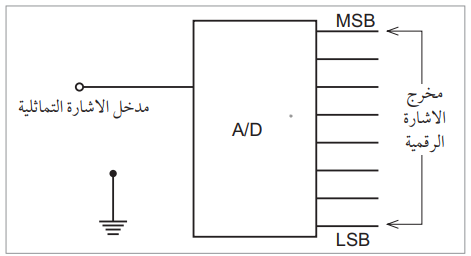

ولكن عندما يتم وصل مجس تماثلي فلا بد من وجود دارة تحويل من إشارة تماثلية إلى إشارة رقمية. وهذه الدارة تقوم بتحويل الإشارة التماثلية إلى إشارة رقمية (ثنائية). وهذا ما يسمى A/D.

وكذلك بعد معالجة الإشارة رقمياً هناك حاجة لإعادتها إلى إشارة تماثلية مرة أخرى وهذا ما يسمى D/A. وبالتالي في دارة التحويل AND يكون مدخل الإشارة تماثلياً والمخرج رقمياً كما في الشكل (1):

شكل (1)

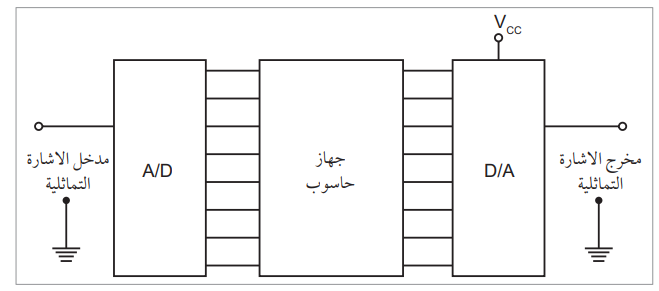

وفي دارة التحويل D/A يكون مدخل الإشارة رقمياً والمخرج تماثلياً كما في الشكل (2):

شكل (2)

وبما أنه يتم استخدام AD وDIA في الأنظمة المختلفة التي تستخدم فيها المجسات والتحكم بعمل معين مثل التحكم بنظام المحرك في السيارة فإنه يمكن تمثيل النظام كما في الشكل (3):

شكل (3)

وبما أنه من السهل تحويل الإشارة الرقمية إلى تماثلية، فسنبدأ بهذا الموضوع ثم تطرق إلى طرق تحويل الإشارة التماثلية إلى رقمية.

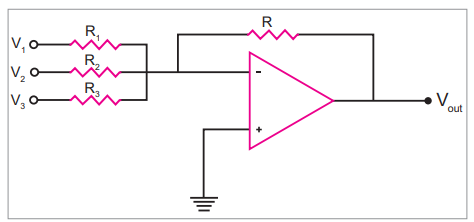

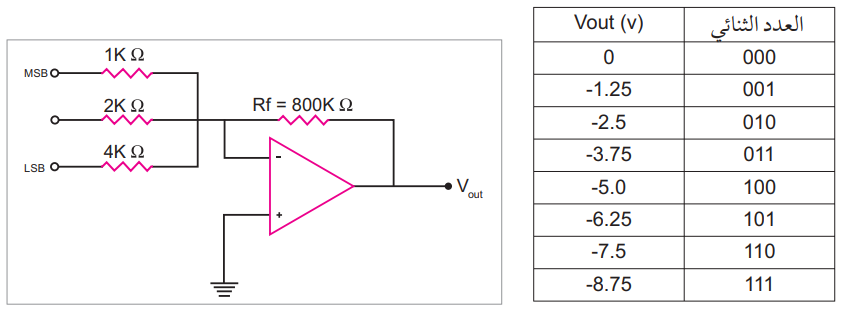

يبين الشكل (4) دارة لتحويل الإشارة الرقمية إلى إشارة تماثلية وهو عبارة عن مكبر عاكس يعمل كجامع باستخدام مضخم العمليات، كما مر معنا في السنة الماضية.

شكل (4)

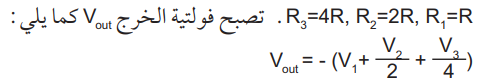

إذا تم تغيير قيم المقاومات، فإنه يتم اختلاف تأثير الفولتيات V1, V2, V3, على فولتية الخرج Vout. لناخذ مثلاً القيم التالية:

لاحظ أن تأثير فولتيات الدخل بدءاً من V1 يكون نصف تأثير الفولتية التي قبلها. أي أن V1 لها تأثير بنسبة 1:1 (کسب 1) بينما V2 لها تأثير بنسبة 2:1 (كسب 12) والفولتية V3 لها (كسب 14).

ولم يات اختيار هذه القيم بشكل عشوائي. حيث إنها تمثل الأوزان المناظرة في نظام العدد الثنائي. (0 1 2 4 ... إلخ).

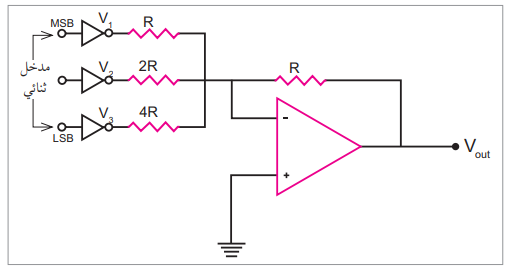

وبالتالي إذا جعلنا على المداخل للجامع العاكس بوابات منطقية لها مخرج V0منطق (0) أو V5 (منطق 1) فإن الدارة تصبح كما في الشكل (5):

شكل (5)

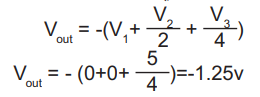

لنأخذ مثلاً الرقم الثنائي 001.

هذا يمثل الفولتيات

0 = ,V3 = 5V1V2 = 0,V

Vout تساوي

وبعمل نفس الشيء لجميع الأرقام، نحصل على النتائج كما الجدول التالي، (الجدول 1):

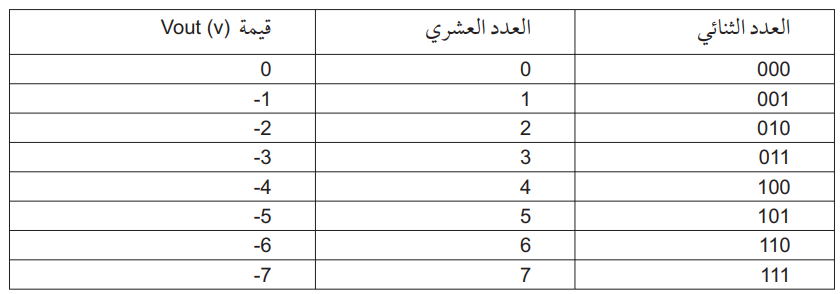

لاحظ أنه مع تغيير العدد الثنائي يكون هناك تغير في فولتية الخرج بمقدار 1.25 فولت. يمكن تعديل قيم المقاومات لنحصل على فولتيات تناظر تماماً قيم الأعداد الثنائية كما في الشكل (6):

الجدول (1) شكل (6)

وبالتالي تصبح قيم الجدول كما يلي:

الجدول (2)

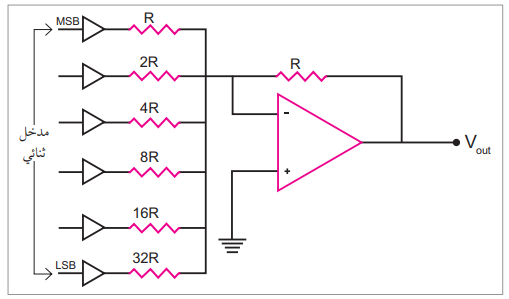

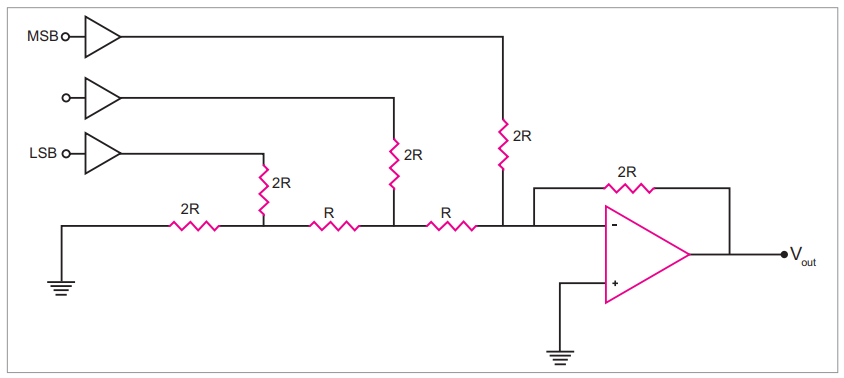

وتسمى هذه الطريقة ب D/A R/2n R. اذا اردنا ان نزيد من دقة هذا D/A (بزيادة عدد المداخل)، نحتاج فقط الى إضافة مقاومات أخرى على المداخل مع الحفاظ على نفس النسبة D/A R/2n R كما في الشكل (7).

شكل (7): 6 خانات D/A

ومن الجدير بالذكر هنا، انه يجب ان تكون الفولتية مخرج جميع البوابات المنطقية متساوية تماما في حالة المنطق (1)، حتى يعمل النظام D/A بالشكل الصحيح.

فلو كان مخرج إحدى البوابات 5.02+ فولتا في حالة المنطق (1) وبوابة أخرى 4.86+ مثلاً فإن مخرج D/A سوف يتأثر بشكل كبير. وكذلك ينطبق هذا الشرط على فولتية مخرج البوابات في حالة المنطق 0 بحيث يجب أن يكون يساوي صفراً تماماً. ولذلك ينصح عادة باستخدام بوابات من نوع CMOS ويتم اختيار المقاومات لتقليل التيار الذي تسحبه أو تخرجه كل بوابة.

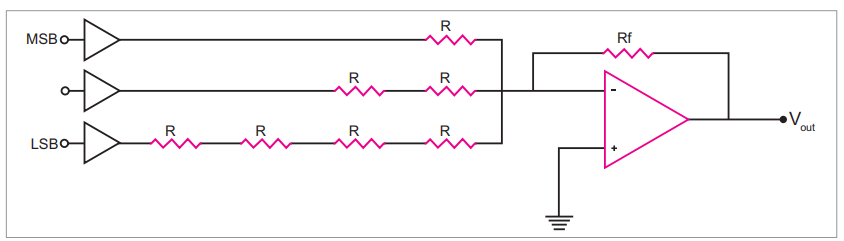

من سيئات الدارة السابقة هو الحاجة إلى قيم فريدة للمقاومات خاصة عند زيادة عدد خانات البيانات الثنائية. إحدى الطرق للتغلب على هذه المشكلة هو وصل مجموعة على التوالي كما في الشكل (8):

شكل (8)

إلا أن هذا الترتيب غير فعال وذلك بسبب الحيز وفقد القدرة الذي سيصبح في الدارة. وللتغلب على ذلك يمكن اعادة ترتيب المقاومات كما في الشكل (9) بحيث تحتاج فقط إلى قيمتين هما R ,2R وتعرف هذه الطريقة بشبكة السلم (Ladder

شكل (9)

ويمكن تحليل هذه الدارة رياضياً، إلا أن ذلك خارج نطاق البحث هنا. وتكون النتيجة كما في الجدول (1). ولكي تناظر قيم Vout الأرقام الثنائية يتم استخدام قيمة Rf = 1.6R وتكون النتيجة كما في الجدول (2).

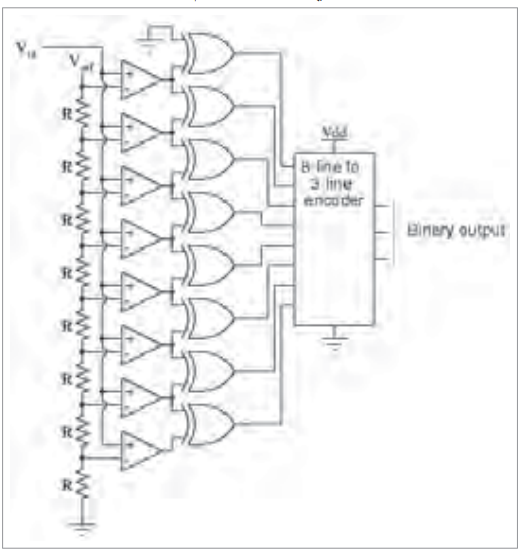

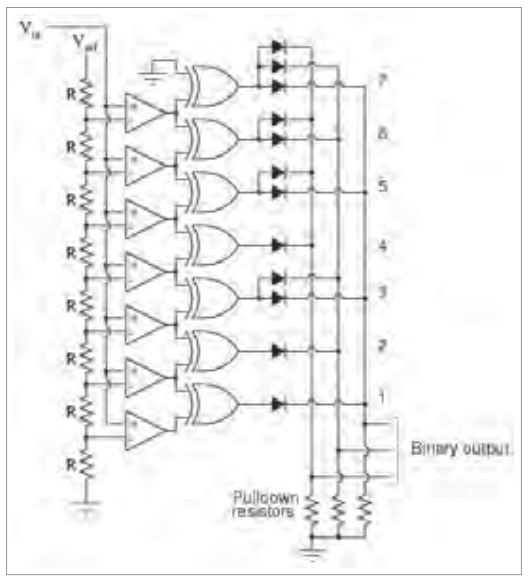

يبين الشكل (10) دارة تحويل من تماثلي إلى رقمي.

شكل (10)

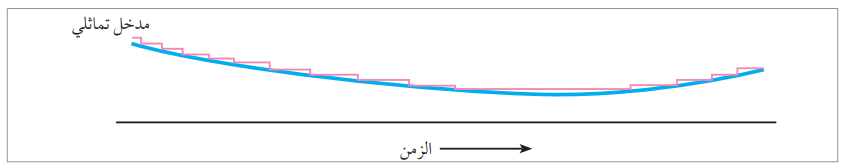

تسمى هذه الدارة بدارة التحويل المتوازي وتعد من أبسط دارات التحويل من تماثلي إلى رقمي. تتكون هذه الدارة من مجموعة من المقارنات بحيث يقوم كل مقارن بمقارنة الإشارة الداخلية إليه مع فولتية مرجعية محدد. يتم تجميع مخارج المقارنات في دارة مرمز ذي أفضلية Priority check encoder)) الذي ينتج إشارة رقمية. وكما هو مبين في الشكل فإن الإشارة الرقمية الناتجة تتكون من 3 خانات. يتم تحديد الفولتية المرجعية Vref عن طريق منظم فولتية دقيق، ويكون هذا جزءاً من الدارة، إلا أنه غير ظاهر في هذا الشكل. عندما يزيد مستوى الإشارة التماثلية عن فولتية المرجعية لكل مقارن، فإن مخرج المقارن سوف يكون في الحالة العالية. وتقوم دارة المرمز بتوليد عدد ثنائي اعتماداً على أعلى فولتية، متجاهلاً الفولتيات الأخرى. لنفرض أن الإشارة التماثلية كما في الشكل (11):

شكل (11)

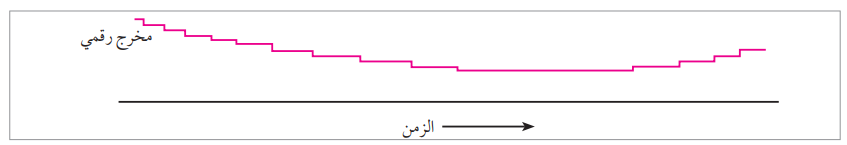

عندما يتم تشغيل النظام يكون شكل الإشارة الخارجة كما في الشكل (12):

شكل (12)

لاحظ أن الإشارة الخارجة تأخذ قيماً منفصلة (discrete) بين أدنى وأعلى مستوى للإشارة التماثلية. وفي هذا المثال تحديداً يمكن الاستغناء عن دارة المرمز نتيجة لطبيعة حالات مخارج المقارنات التتابعية. (كل مقارن يصل إلى حالة الاشباع بالتتابع من الأدنى إلى الأعلى). وهذا الأثر يمكن تحقيقه من خلال مجموعة من بوابات الاستثناء (XOR)، وبالتالي يمكن استخدام مرمز بدون أفضلية. كما في الشكل (13).

شكل (13)

وكذلك فإن دارة المرمز يمكن عملها من مصفوفة ثنائيات وعليه تصبح الدارة النهائية كما في الشكل (14). إن هذا النوع من A/D هو الأبسط من حيث نظرية العمل، وكذلك الأكثر فعالية بين الأنواع الأخرى من حيث السرعة.

ولكن أحد مساوئه هو عدد المقارنات المستخدمة، وكذلك زمن التأخير الذي يحدث في البوابات. لاحظ أنه في حالة 4 خانات تحتاج إلى 16 مقارن. وبما أن عدد الخانات المطلوبة من A/D هو 8 عادة، فإن عدد المقارنات المطلوبة يصبح -256 وبالتالي فإن هذه الطريقة تصبح غير مجدية في مثل هذه الحالة.

شكل (14)

وهناك أنواع أخرى، لا مجال للتطرق إليها في هذا الكتاب.

ومن الدارات المشهورة في التحويل من إشارة تماثلية إلى إشارة رقمية الدارة المتكاملة TLC549 التي تأخذ معطيات تسلسلية، ولها ثماني خانات على المخرج.

|

|

|

|

دخلت غرفة فنسيت ماذا تريد من داخلها.. خبير يفسر الحالة

|

|

|

|

|

|

|

ثورة طبية.. ابتكار أصغر جهاز لتنظيم ضربات القلب في العالم

|

|

|

|

|

|

|

قسم شؤون المعارف ووفد من جامعة البصرة يبحثان سبل تعزيز التعاون المشترك

|

|

|